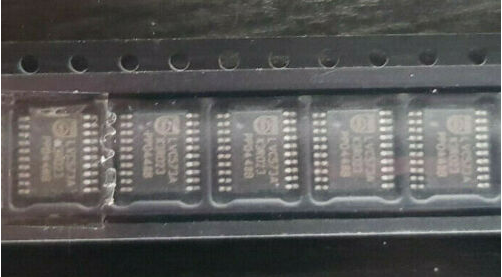

74LVC573A

|

5PCS x 74LVC573A

Footprint: TSSOP-20

Octal D-type transparent latch with 5 V tolerant inputs/outputs; 3-state The 74LVC573A is an 8-bit D-type transparent latch with 3-state outputs. The device features latch enable (LE) and output enable (OE) inputs. When LE is HIGH, data at the inputs enter the latches. In this condition the latches are transparent, a latch output will change each time its corresponding D-input changes. When LE is LOW the latches store the information that was present at the inputs a set-up time preceding the HIGH-to-LOW transition of LE. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE input does not affect the state of the latches. Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of these devices as translators in mixed 3.3 V and 5 V environments. Schmitt-trigger action at all inputs makes the circuit tolerant of slower input rise and fall times. |